1)实验平台:正点原子开拓者FPGA开发板

第五十二章基于FIRIP核的低通滤波器实验

FIR滤波器是有限冲激响应(FiniteImpulseResponse)滤波器的简称,它与IIR(InfiniteImpulse

Response,无限冲击响应)滤波器,都是按照单位冲击响应h(n)的时间特性分类的两种基本

还具有线性相位延迟的特点。因此FIR滤波器在通信、图像处理、模式识别等领域都有着广泛

的应用。本章我们将使用QuartusII软件里的FIRCompilerIP核,来对音频信号进行滤波,作

为一个简单的例程,向大家介绍AlteraFIRCompilerIP核的使用方法。

本章包括以下几个部分:

52.1FIRCompilerIP核简介

52.2实验任务

52.3硬件设计

52.4程序设计

52.5下载验证

FIRCompiler核简介

我们日常生活中经常用到的音乐播放器、手机、数码相机等电子设备中,都可以看到数字

信号处理(DSP)的使用。而FIR滤波器因为系统稳定、易实现线性相位和允许多通道滤波等

特点,在数字信号处理领域受到广泛运用。

由于FIR滤波器处理的是数字信号,所以模拟信号在进入FIR滤波器前,需要先经过AD

器件进行模数转换,将模拟信号转化为数字信号。而为了让信号处理不发生失真,信号的采样

速度必须满足奈奎斯特定理,一般取信号最高频率的4到5倍做为采样频率。

FIR滤波器信号处理如下公式所示,其中x(n)是输入的信号,h(n)为FIR滤波系数,

y(n)为滤波后的信号。N为FIR滤波器的抽头数,滤波器阶数为N-1。

(n)=∑ℎ()×(−)

−1

=0

由上面的公式得到的一种FIR滤波器实现结构如下图所示,主要由延迟单位−1、乘法器、

累加器组成。这种滤波器被称为直接型FIR滤波器。

图52.1.1直接型FIR滤波器

接下来我们举个简单的例子,下图所示为一个低通滤波器的频率响应图,通带(滤波器允

许通过信号的频率范围)边缘频率为3Hz,阻带(信号幅度衰减到极低水平的频率范围)边缘

频率为5Hz,3Hz到5Hz之间为过渡带。信号衰减3dB所对应的信号频率即为截止频率。

图52.1.2一个低通滤波器频率响应曲线

我们在前面的内容里展示了FIR滤波器的信号处理公式、基本实现结构、频率响应曲线图。

而FIR滤波器的具体实现涉及到数字信号处理相关的专业知识内容,这里则主要讲解如何创建

我们需要的FIR滤波器。接下来我们了解一下设计一个简单的FIR滤波器需要设置的参数。

一个简单的FIR滤波器需要设置的参数:

1)FilterType(滤波器类型):设置FIR滤波器的类型:低通(Lowpass)、高通(high

pass)、带通(bandpass)以及带阻(bandstop)等。下图所示为FilterType选项栏

的下拉选项。

图52.1.3选择滤波器类型

四种基础滤波器允许通过的信号频率如下图所示:

图52.1.4四种基础滤波器的频率响应曲线

2)WindowType(窗函数类型):FIR滤波器的设计方法有很多种。常用的有窗函数设计

法(Window)、等波纹设计法(Equiripple)和最小二乘法(Least-Squares)等。Quartus

II软件里的FIRCompilerIP核提供的设计方法是窗函数设计法。我们可以选择的窗函数有矩形窗(Rectangular)、汉宁窗(Hanning)、哈明窗(Hamming)、布莱克曼窗

(Blackman)。这里只需要简单了解一下有这些窗函数即可。不同的窗函数有各自对

应阻带最小衰减、过渡带宽等特性,这些都是设计滤波器时比较重要的参数。阻带衰

减dB数越大,对阻带信号的抑制作用越好。过渡带宽与滤波器的阶数计算有关。旁

在FrequenceResponse窗口看到窗函数的频率响应曲线。

图52.1.5窗函数特性表

图52.1.6选择窗函数

3)Coefficient(抽头系数):抽头系数是滤波器系数的个数。而滤波器的阶数比抽头数小

1。滤波器的阶数直接影响滤波器的性能,阶数越高,性能越好,相应在FPGA中实现

该滤波器耗用的资源越多。我们需要手动输入数值来确定系数。

图52.1.7输入抽头系数

4)SampleRate(采样率):输入数据的采样率,与AD的采样速率保持一致,单位为SPS(每

秒采样次数SamplesperSecond)。其中4.8E4表示为4.8×104,也就是48K。

图52.1.8设置采样率

5)CutoffFreq(截止频率):用于设置通过信号的频率界限。如图为低通滤波器时,截止

频率则只有一个。当保持输入信号的幅度不变,改变频率使输出信号降至最大值的

0.707倍,即用频响特性来表述即为-3dB点处即为截止频率,它是用来说明频率特性

指标的一个特殊频率。

图52.1.9设置截止频率

6)InputBitWidth(输入数据位宽)CoefficientBitWidth(位宽):输入位宽指的是滤

波器输入数据数据的位宽,系数位宽为滤波器的系数位宽,这两个位宽一起决定了滤

波器输出数据的位宽。

图52.1.10设置输入数据位宽及滤波器系数位宽

实验任务

本节实验任务是在“基于FFTIP核的音频频谱仪实验”的基础上,添加一个FIR低通滤

波器,并通过按键来选择是否使用低通滤波器对WM8978输出的信号进行滤波,然后使用Altera

FFTIP核分析WM8978输出的音频信号的频谱,并将频谱的幅度特性显示到4.3寸RGBTFT

LCD上。

硬件设计

本实验的硬件设计原理与“基于FFTIP核的音频频谱仪实验”完全相同,请参考“基于

FFTIP核的音频频谱仪实验”中的硬件设计部分。

程序设计

图51.4.1是根据本章实验任务画出的系统框图。对比于“基于FFTIP核的音频频谱仪

实验”,我们在“基于FFTIP核的音频频谱仪实验”的系统框图中添加了一个配置为低通滤

波器的FIR模块。当我们没有触碰开发板上的KEY0按键的时候,WM8978模块输出的音频数据

先经过FIR模块进行滤波,然后通过FFT模块做频谱分析,得到频谱幅度数据。当我们按下按

键的时候,WM8978模块输出的音频数据则直接通过FFT模块做频谱分析,得到我们需要的频

谱幅度数据。得到的数据经过LCD模块处理后,转变成频谱幅度图像,显示在RGBTFT-LCD上。

图52.4.1IP核之FFT实验系统框图

程序中各模块端口及信号连接如图51.4.2所示:

图52.4.2模块连接图

FPGA顶层(FFT_audio_lcd)例化了以下五个模块:pll时钟模块(pll)、wm8978模块

(wm8978_ctrl)、FIR模块(fir_lowpass)、FFT模块(FFT_top)、LCD模块(LCD_top)。

pll时钟模块(pll):本实验中WM8978模块所需要的时钟为12MHz,FFT模块的驱动时钟为

50MHz,另外LCD模块需要50Mhz的时钟来处理、缓存FFT模块输出的数据,并在10MHz的驱动时

钟下驱动RGBTFT-LCD显示。因此需要一个PLL模块用于产生系统各个模块所需的时钟频率。

wm8978模块(wm8978_ctrl):WM8978控制模块主要完成WM8978的配置和WM8978接

收的录音音频数据的接收处理,以及FPGA发送的音频数据的发送处理。有关该模块的详细介

绍请大家参考“基于FFTIP核的音频频谱仪实验”章节。

FIR模块(fir_lowpass):FIR模块负责对输入的音频数据进行低通滤波。

FFT模块(FFT_top):FFT模块将wm8978模块传输过来的音频信号进行缓存,然后将其

送给FFTIP核进行频谱分析。接着计算FFTIP核输出复数的平方根,即频谱的幅度值,然后

将其输出给LCD模块显示。有关该模块的详细介绍请大家参考“基于FFTIP核的音频频谱仪

实验”章节。

LCD模块(LCD_top):LCD模块取FFT模块传输过来的一帧数据的一半(也就是64个数

据)进行缓存,并驱动RGBTFT-LCD液晶屏显示频谱。有关该模块的详细介绍请大家参考“基

于FFTIP核的音频频谱仪实验”章节。

顶层模块的代码如下:

1moduleFIR_audio_lcd(

2inputsys_clk,

3inputrst_n,

4

5//WM8978接口

6outputaud_mclk,//WM8978接口

7inputaud_bclk,

8inputaud_lrc,

9inputaud_adcdat,

10outputaud_dacdat,

11outputaud_scl,

12inoutaud_sda,

13//LCD接口

14outputlcd_hs,//LCD行同步信号

15outputlcd_vs,//LCD场同步信号

16outputlcd_de,//LCD数据输入使能

17output[15:0]lcd_rgb,//LCDRGB565颜色数据

18outputlcd_bl,//LCD背光控制信号

19outputlcd_rst,//LCD复位信号

20outputlcd_pclk,//LCD采样时钟

21

22inputkey0//KEY0:按下时显示原始音频频谱,释放后显示滤波后频谱

23);

24

25//wiredefine

26wirefft_sop;

27wirefft_eop;

28wirefft_valid;

29wire[15:0]fft_data;

30wireaudio_valid;

31wire[15:0]audio_data;

32wireclk10M;

33wire[15:0]audio_data_out;

34wire[33:0]fir_odata_w;

35wirefir_dvalid_w;

36

37//*****************************************************

38//**maincode

39//*****************************************************

40

41//锁相环输出FFT、WM8978、LCD等模块的驱动时钟

42pllpll_inst(

43.inclk0(sys_clk),

44.c0(aud_mclk),

45.c1(clk50M),

46.c2(clk10M)

47);

48

49//例化WM8978控制模块

50wm8978_ctrlu_wm8978_ctrl(

51//systemclock

52.clk(clk50M),//时钟信号

53.rst_n(rst_n),//复位信号

54//wm8978interface

55//audiointerface(mastermode)

56.aud_bclk(aud_bclk),//WM8978位时钟

57.aud_lrc(aud_lrc),//对齐信号

58.aud_adcdat(aud_adcdat),//音频输入

59.aud_dacdat(aud_dacdat),//音频输出

60//controlinterface

61.aud_scl(aud_scl),//WM8978的SCL信号

62.aud_sda(aud_sda),//WM8978的SDA信号

63//userinterface

64.dac_data(audio_data_out),//输出的音频数据

65.adc_data(audio_data),//输入的音频数据

66.rx_done(audio_valid),//一次接收完成

67.tx_done()//一次发送完成

68);

69

70assignaudio_data_out=key0?fir_odata_w[33:18]:audio_data;

71

72fir_lowpassu_fir_lowpass(

73.clk(aud_bclk),

74.reset_n(rst_n),

75

76.ast_sink_data(audio_data),

77.ast_sink_valid(audio_valid),

78.ast_sink_error(),

79.ast_sink_ready(),

80

81.ast_source_ready(1'b1),

82.ast_source_data(fir_odata_w),

83.ast_source_valid(fir_dvalid_w),

84.ast_source_error(),

85);

86

87//利用ip核实现的FFT

88FFT_topFFT_u(

89.clk_50m(clk50M),

90.rst_n(rst_n),

91

92.audio_clk(aud_bclk),

93.audio_valid(fir_dvalid_w),

94.audio_data(audio_data_out),

95

96.data_sop(fft_sop),

97.data_eop(fft_eop),

98.data_valid(fft_valid),

99.sqrt_data(fft_data)

100);

101

102//MCU_LCD显示模块

103LCD_topLCD_u(

104.clk50M(clk50M),

105.rst_n(rst_n),

106.clk10M(clk10M),

107

108.lcd_hs(lcd_hs),

109.lcd_vs(lcd_vs),

110.lcd_de(lcd_de),

111.lcd_rgb(lcd_rgb),

112.lcd_bl(lcd_bl),

113.lcd_rst(lcd_rst),

114.lcd_pclk(lcd_pclk),

115

116.fft_valid(fft_valid),

117.fft_sop(fft_sop),

118.fft_eop(fft_eop),

119.fft_data(fft_data)

120);

121

122module

相比于“基于FFTIP核的音频频谱仪实验”,基于FIRIP核的低通滤波器实验只是在顶

至第85行,及第70行所示。接下来我们来讲解如何创建及使用FIR低通滤波器。

我们在QuartusII软件的菜单栏中找到【Tools】→【MegaWizardPlug-InManager】按钮并

图52.4.3工具栏打开IP核界面

图52.4.4创建IP核向导页面

在该页面中,可以看到有三个选项,第一个是创建一个新的IP核,第二个是编辑一个已

经创建好的IP核,第三个是复制一个已经创建好的IP核。因为我们这里是首次创建IP核,因

图52.4.5选择FIRCompilerIP核界面

在该页面中,我们可以在DSP/Filters下找到核,也可以直接在搜索框

中输入fir找到它。我们找到核以后,单击选中它,然后我们需要为ALTPLL

IP核选择保存的路径及名称,我们在工程路径par/ipcore文件夹下新建一个FIR文件夹,用于

存放工程中用到的IP核,然后在“Whatnamedoyouwantfortheoutputfile”一栏中输入IP存放

的路径及名称,这里我们命名为fir_lowpass并且选择创建的IP核代码为VerilogHDL。需要注

意的是,如果想要对IP核进行仿真,需要将IP核存放目录设置为目录,也就是将IP核存放在

图52.4.6FIRIP核主界面

Parameterize,进入如下所示的界面,对IP核进行参数配置。

图52.4.7FIRIP核配置界面

由于核处理的是wm8978输出一路16位有符号数数据。所以,Number

ofinputchannels选项(输入通道数)保持为1;InputNumberSystem选项(输入数据系统)

保持为SignedBinary;InputBitWidth(输入位宽)选项设置为16;输出基于实际的系数(Actual

Coefficients),也就是与InputBitWidth(输入位宽)和BitWidth(系数)其它选项保持默认

图52.4.8IP核参数设置界面

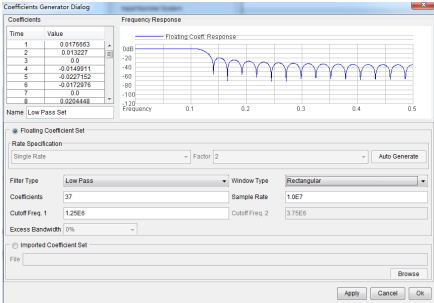

本次实验中,我们需要设置的是低通滤波器,于是FilterType(滤波器类型)保持LowPass

不变;由于wm8978的采样速率为48K,所以SampleRate设置为4.8E4;Coefficients(抽头系

数)越大,滤波的效果越好,但是耗用的资源越多,这里设置数值为32;本次实验将使用到低

通滤波器,于是暂设置截止频率为5KHz,在框中输入5E3;接下来就要选择要用

到的窗函数了。窗函数选项栏里默认的是矩形窗(Rectangular)。根据实际需要,选择符合需

求的窗函数即可,没有固定的选项。WindowType(窗函数类型)选项栏中共有4个选项,选

函数的滤波器频率响应曲线。然后根据四种频率响应曲线选择最符合需求的窗函数。这里因为

Hamming(哈明窗)的频率响应曲线到达截止频率时,衰减了60dB左右,且频率响应曲线下

降得更快。所以在WindowType选项栏中选择Hamming窗函数。设置完成后的界面如下所示。

图52.4.9设置完成后的界面

现在讲解一下频率响应图中横纵坐标代表的物理意义,其中的横坐标Frequency表示的是

归一化频率,纵坐标dB代表的是衰减指标。我们知道采样频率的一半为奈奎斯特频率,而归

一化频率=

真实频率

奈奎斯特频率

。所以图中的0.1代表的是48KHz÷2×0.1=2.4KHz;衰减指标定义为20log

(Vout/Vin)。图中-20dB对应的是:20log(Vout/Vin)=-20,因此Vout=0.1Vin,所以信号幅

值衰减到原来幅度的0.1。

多次最终就能生成成功。

图52.4.10生成滤波器文件选项

图52.4.11滤波器生成界面

与生成了。

图52.4.12滤波器生成成功界面

接下来我们来了解一下怎么使用这个IP核。我们在顶层代码的第72行至第85行例化了

FIRCompiler核,代码如下所示。

72fir_lowpassu_fir_lowpass(

73.clk(aud_bclk),

74.reset_n(rst_n),

75

76.ast_sink_data(audio_data),

77.ast_sink_valid(audio_valid),

78.ast_sink_error(),

79.ast_sink_ready(),

80

81.ast_source_ready(1'b1),

82.ast_source_data(fir_odata_w),

83.ast_source_valid(fir_dvalid_w),

84.ast_source_error(),

85);

信号定义如下表所示,与FFTIP核一样,都是Avalon-ST数据接口。

图52.4.13滤波器信号描述

时序图如下所示,一直保持ast_source_ready信号为高电平。在复位信号reset_n信号、

ast_sink_ready为高电平的时候,拉高ast_sink_valid信号,并给FIR滤波器输入数据,滤波器

就开始处理数据了。当滤波器拉高ast_source_valid信号的时候,FIR滤波器就开始输出滤波处

理后的数据。

图52.4.14滤波器工作时序图

可以看到在代码第75行至85行,为了降低操作IP核的难度,没有理会ast_sink_ready信

号的状态,如代码第79行所示。

下载验证

首先我们打开基于FIRIP核的低通滤波器实验工程,在工程所在的路径下打开

FIR_audio_lcd\par文件夹,在里面找到“FIR_audio_”并双击打开。注意工程所在

的路径名只能由字母、数字以及下划线组成,不能出现中文、空格以及特殊字符等。工程打开后如图1.5.1示:

图52.5.1IP核之FIR实验工程

将下载器一端连接电脑,另一端与开发板上对应端口连接,然后用音频线连接电脑和开发

板,最后连接电源线并打开电源开关。

FIR_audio_lcd\par\output_files目录下的“FIR_audio_”文件。开发板电源打开后,在

图所示:

图52.5.2下载界面

然后,打开FIR_audio_lcd\音频文件目录下的noise_96文件,我们可以在LCD上

看到如下图所示经过FIR滤波器滤波后的频谱图:

图52.5.3频谱图

按下按键后,频谱幅度图像如下所示,未经过滤波的幅度图像的噪声要大很多。

图52.5.4未经滤波的频谱幅度图